# ELECTRONIC AND ELECTRICAL ENGINEERING

PRINCIPLES AND PRACTICE

# **Electronic and Electrical Engineering**

Principles and Practice

Third edition

**Lionel Warnes**

© L. A. A. Warnes 1994, 1998, 2003

All rights reserved. No reproduction, copy or transmission of this publication may be made without written permission.

No paragraph of this publication may be reproduced, copied or transmitted save with written permission or in accordance with the provisions of the Copyright, Designs and Patents Act 1988, or under the terms of any licence permitting limited copying issued by the Copyright Licensing Agency, 90 Tottenham Court Road, London W1T 4LP.

Any person who does any unauthorised act in relation to this publication may be liable to criminal prosecution and civil claims for damages.

The author has asserted his right to be identified as the author of this work in accordance with the Copyright, Designs and Patents Act 1988.

First edition 1994

Second edition 1998

Third edition 2003

Published by

PALGRAVE MACMILLAN

Houndmills, Basingstoke, Hampshire RG21 6XS and

175 Fifth Avenue, New York, N. Y. 10010

Companies and representatives throughout the world

PALGRAVE MACMILLAN is the global academic imprint of the Palgrave Macmillan division of St. Martin's Press, LLC and of Palgrave Macmillan Ltd. Macmillan® is a registered trademark in the United States, United Kingdom and other countries. Palgrave is a registered trademark in the European Union and other countries.

ISBN 978-0-333-99040-7 ISBN 978-0-230-21633-4 (eBook) DOI 10.1007/978-0-230-21633-4

This book is printed on paper suitable for recycling and made from fully managed and sustained forest sources.

A catalogue record for this book is available from the British Library.

10 9 8 7 6 5 4 3 2 1 12 11 10 09 08 07 06 05 04 03

# **Contents**

|            |                                                   |           | ۔ ا             | • • •                                 |            |

|------------|---------------------------------------------------|-----------|-----------------|---------------------------------------|------------|

| Physi      | cal constants                                     | ix        | <b>6</b><br>6.1 | Semiconductors Electrons and holes in | 129        |

| Unit n     | prefixes                                          | ix        |                 | semiconductors                        | 129        |

| ۲          |                                                   | .,,       | 6.2             | Electrical conductivity               | 130        |

| Units      |                                                   | X         | 6.3             | The p-n junction                      | 133        |

|            |                                                   |           | 6.4             | A glossary of terms Problems          | 134<br>136 |

| 1          | Circuit analysis                                  | 1         |                 | FIODICITIS                            | 130        |

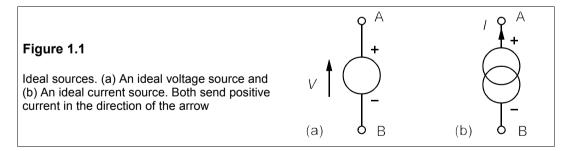

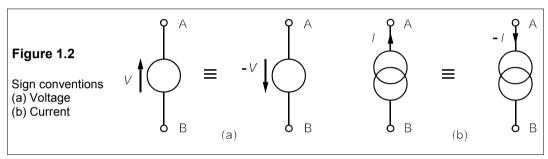

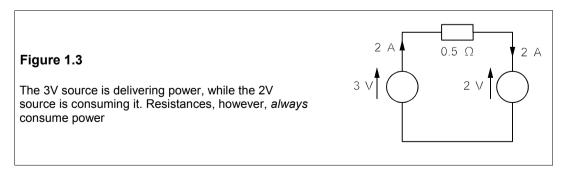

| 1.1        | Sources                                           | 1         | 7               | Diodes                                | 137        |

| 1.2        | Passive circuit elements                          | 3         | 7.1             | Junction diodes                       | 137        |

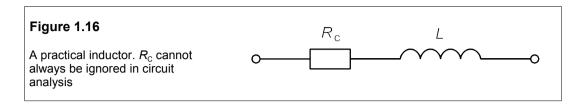

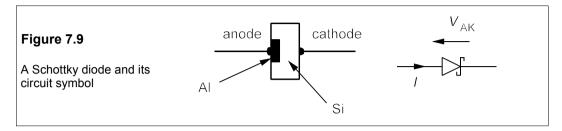

| 1.3        | Practical circuit elements                        | 8         | 7.2             | Schottky diodes                       | 143        |

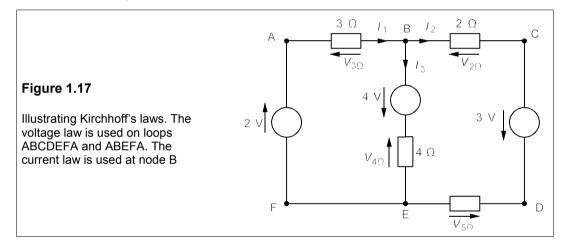

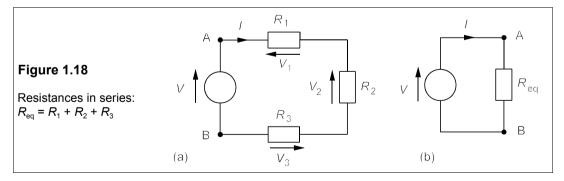

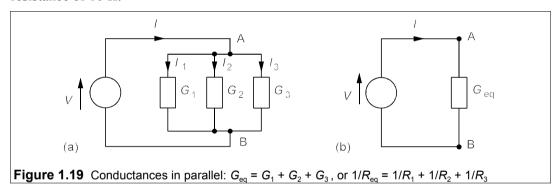

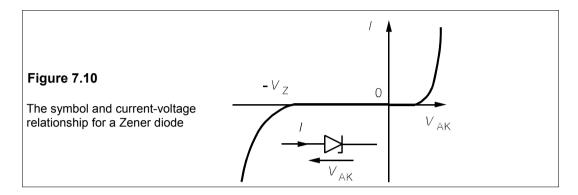

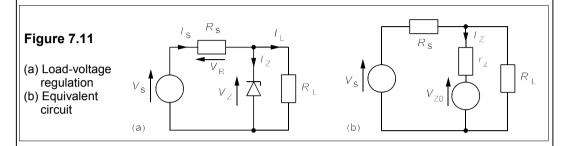

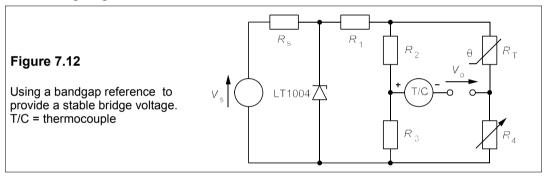

| 1.4        | Circuit analysis and Kirchhoff's laws             | 13        | 7.3             | Zener diodes                          | 145        |

| 1.5        | Circuit theorems and transformations              |           | 7.4             | Light-emitting diodes (LEDs)          | 147        |

| 1.6<br>1.7 | Power and energy Mesh analysis and nodal analysis | 27<br>30  | 7.5             | Solar cells                           | 149        |

| 1.7        | Problems                                          | 35        | 7.6             | Applications for ordinary p-n         |            |

|            |                                                   |           |                 | junction diodes                       | 151        |

| 2          | Sinusoidally-excited circuits                     | 39        |                 | Problems                              | 157        |

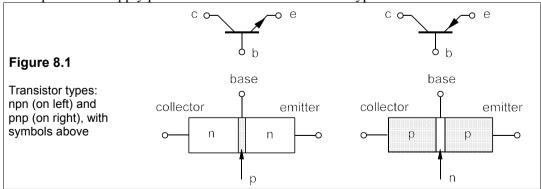

| 2.1        | Sinusoidal excitation                             | 39        | 8               | Bipolar junction transistors          | 161        |

| 2.2        | Phasors                                           | 47        | 8.1             | Theory of operation                   | 161        |

| 2.3        | Circuit analysis with AC                          | 50        | 8.2             | The common-emitter amplifier          | 163        |

| 2.4<br>2.5 | Power in AC circuits Resonant circuits            | 58<br>62  | 8.3             | The emitter follower, or common-      |            |

| 2.5        | Problems                                          | 67        |                 | collector amplifier                   | 174        |

|            | Toblemo                                           | 01        | 8.4             | BJT switches                          | 176        |

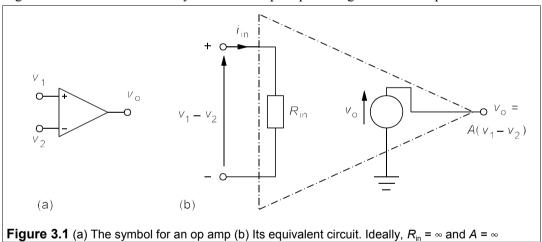

| 3          | Operational amplifiers                            | 71        | 8.5             | BJT specifications Problems           | 177<br>178 |

| 3.1        | The golden rules                                  | 71        |                 | FIODICITIS                            | 170        |

| 3.2        | Some common op amp circuits                       | 72        | 9               | Field-effect transistors              | 181        |

| 3.3        | Analogue computing                                | 75<br>70  | 9.1             | The junction field-effect transistor  |            |

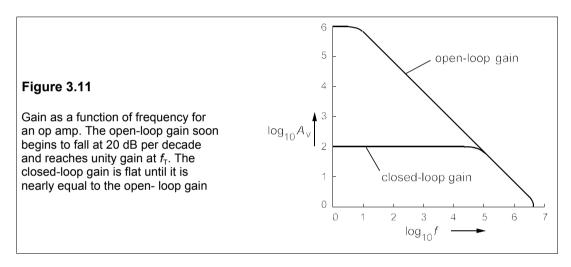

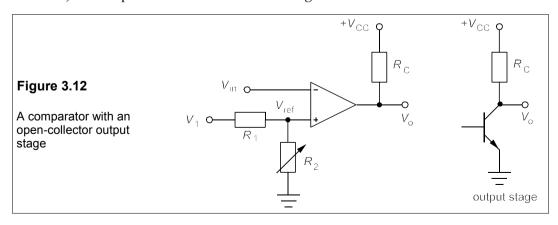

| 3.4<br>3.5 | Practical op amps<br>Comparators                  | 76<br>80  |                 | (JFÉT)                                | 182        |

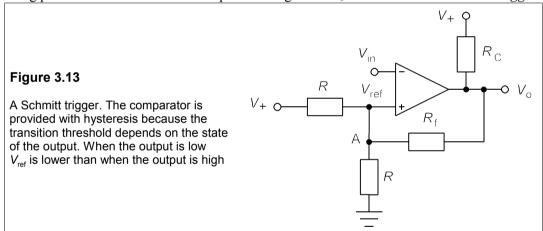

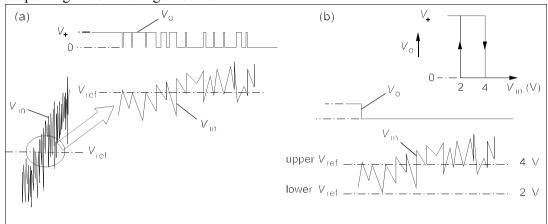

| 3.6        | Schmitt triggers                                  | 81        | 9.2             | The practical common-source           |            |

| 0.0        | Problems                                          | 82        | 9.3             | amplifier<br>MOSFETs                  | 184<br>187 |

|            |                                                   |           | 9.3             | Specifications of some popular        | 101        |

| 4          | Transients                                        | 85        | J.4             | FETs                                  | 189        |

| 4.1        | Transients in RC and RL circuits                  | 85        |                 | Problems                              | 190        |

| 4.2        | Transient analysis by the Laplace                 | 04        |                 |                                       |            |

| 4.3        | transformation Transients in RLC circuits         | 91<br>104 | 10              | Integrated circuits                   | 193        |

| 4.0        | Problems                                          | 109       | 10.1            | Integrated circuit fabrication        | 194        |

|            |                                                   |           | 10.2            | Hybrid circuits Problems              | 198<br>199 |

| 5          | Bode diagrams and 2-port                          |           |                 | Problems                              | 199        |

|            | -                                                 | 111       | 11              | Analogue circuits                     | 201        |

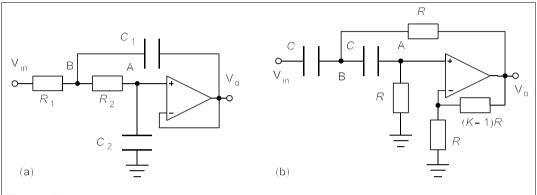

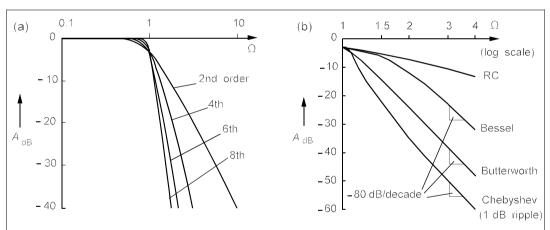

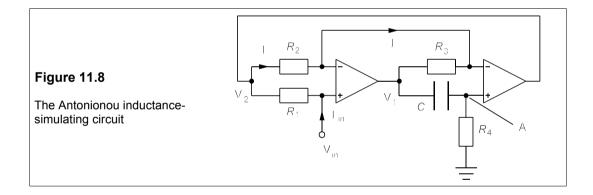

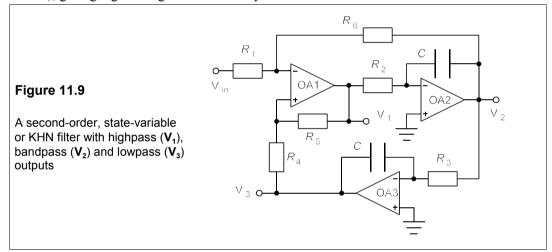

| 5.1        | The steady-state frequency                        |           | 11.1            | Filters                               | 201        |

|            | response of circuits                              | 111       | 11.2            | Oscillators                           | 211        |

| 5.2        | Two-port networks                                 | 119       | 11.3            | Phase-locked loops                    | 216        |

|            | Problems                                          | 126       | 114             | Waveform-generator ICs                | 219        |

vi Contents

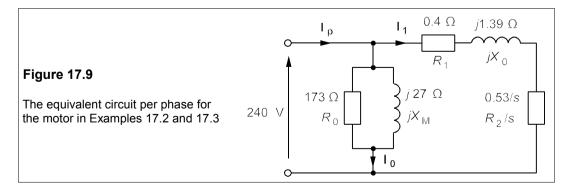

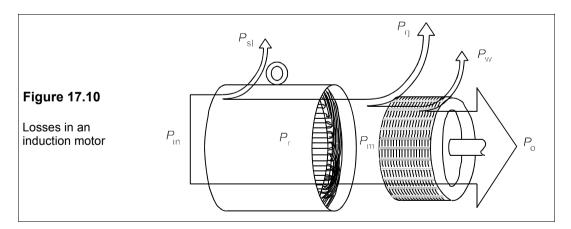

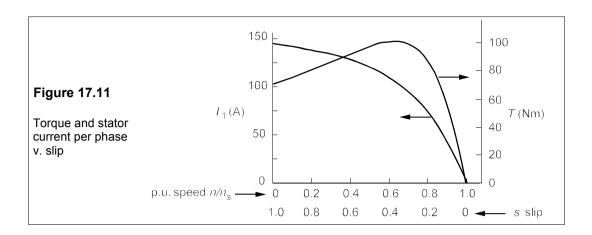

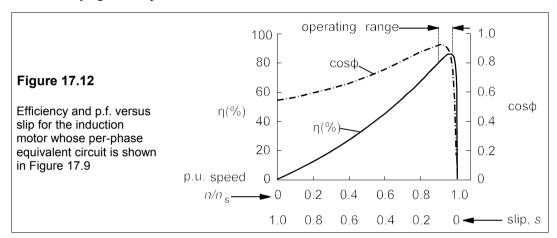

| 11.5                                                                                                                           | Voltage regulators                                                                                                                                                                                                                                                                                                                                                                       | 220                                                                                                                        | 17.3                                                                                                 | Slip                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 320                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

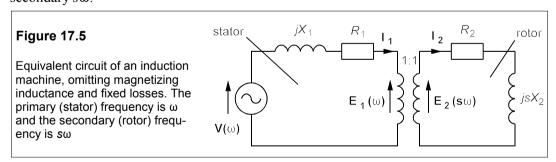

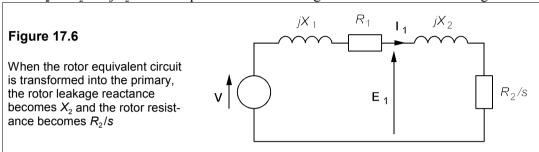

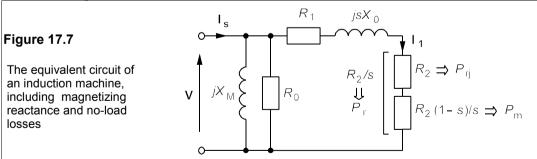

| 11.6                                                                                                                           | Analogue-to-digital (A/D) and digital-to-analogue (D/A) converters                                                                                                                                                                                                                                                                                                                       |                                                                                                                            | 17.4                                                                                                 | The equivalent circuit of an induction machine                                                                                                                                                                                                                                                                                                                                                                                                                          | 322                                                                                                   |

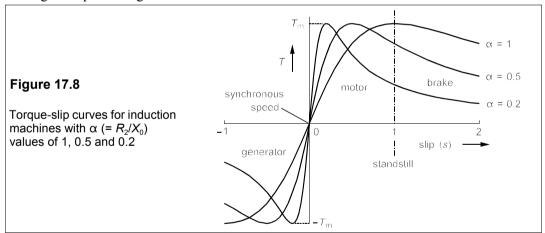

|                                                                                                                                | Problems                                                                                                                                                                                                                                                                                                                                                                                 | 224                                                                                                                        | 17.5                                                                                                 | Torque and slip in an induction machine                                                                                                                                                                                                                                                                                                                                                                                                                                 | 323                                                                                                   |

| 12                                                                                                                             | Power amplifiers, power                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            | 17.6                                                                                                 | Evaluating the components of the equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                     | 324                                                                                                   |

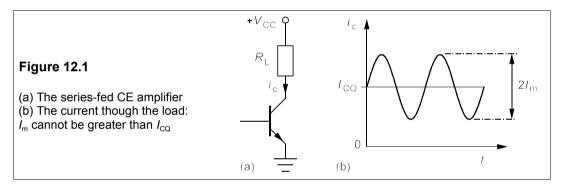

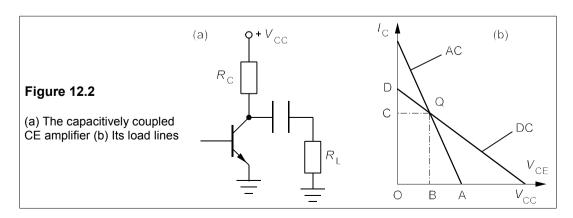

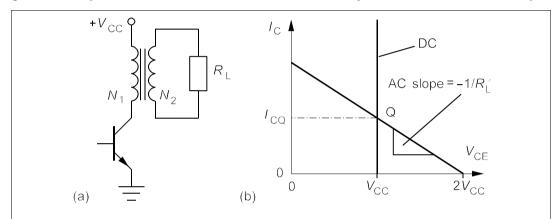

| 12.1                                                                                                                           | supplies and batteries Class-A amplifiers                                                                                                                                                                                                                                                                                                                                                | <b>227</b> 227                                                                                                             | 17.7                                                                                                 | Power and efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 327                                                                                                   |

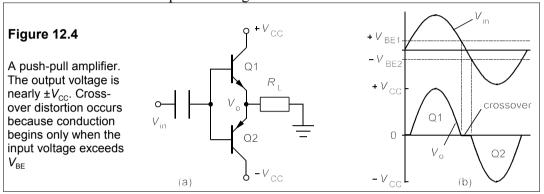

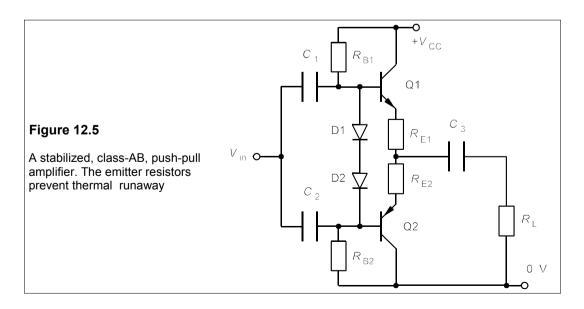

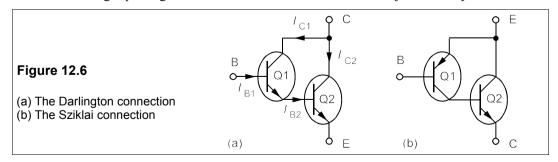

| 12.1                                                                                                                           | Class-B amplifiers                                                                                                                                                                                                                                                                                                                                                                       | 231                                                                                                                        | 17.8                                                                                                 | Practical induction machines                                                                                                                                                                                                                                                                                                                                                                                                                                            | 330                                                                                                   |

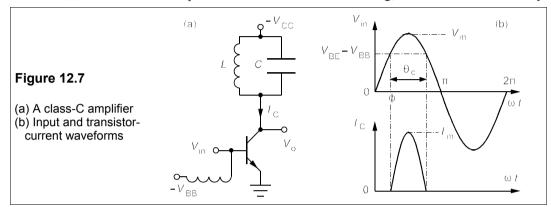

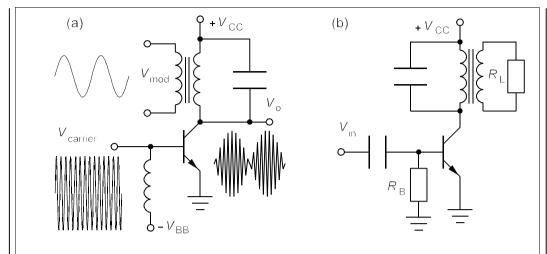

| 12.3                                                                                                                           | Class-C amplifiers                                                                                                                                                                                                                                                                                                                                                                       | 233                                                                                                                        | 17.9                                                                                                 | Domestic-supply induction motors                                                                                                                                                                                                                                                                                                                                                                                                                                        | 333                                                                                                   |

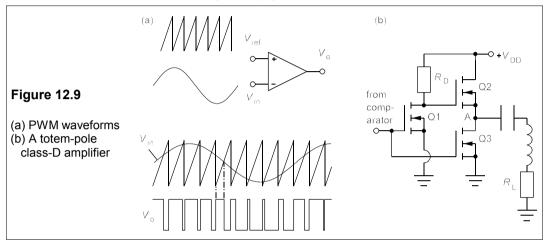

| 12.4                                                                                                                           | Class-D amplifiers                                                                                                                                                                                                                                                                                                                                                                       | 235                                                                                                                        |                                                                                                      | Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 335                                                                                                   |

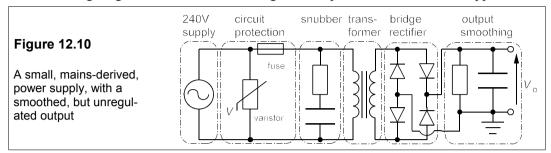

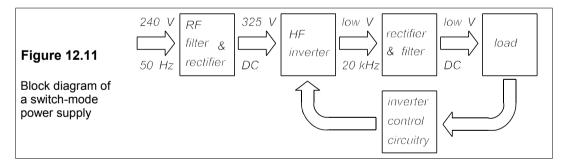

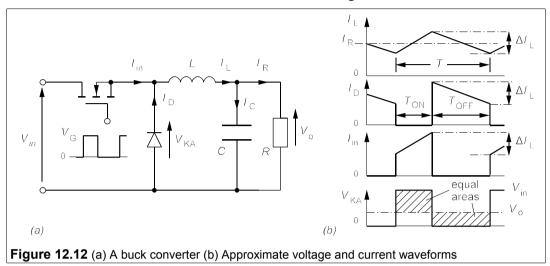

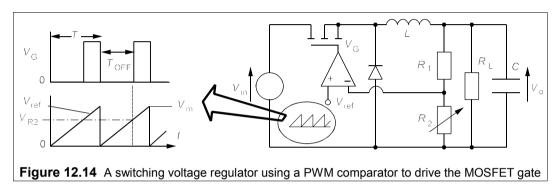

| 12.5<br>12.6                                                                                                                   | Power supplies Switch-mode power supplies                                                                                                                                                                                                                                                                                                                                                | 236<br>238                                                                                                                 | 18                                                                                                   | Synchronous machines                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 337                                                                                                   |

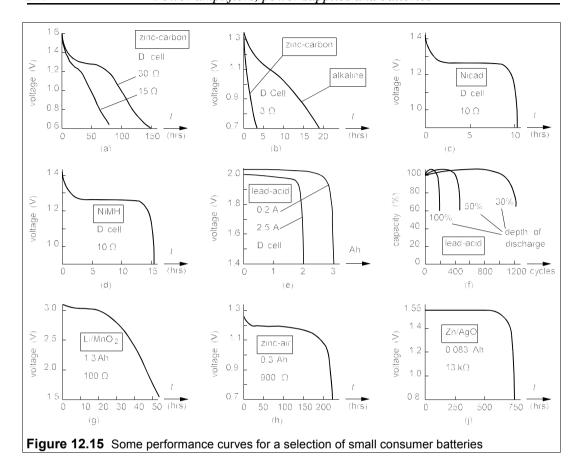

| 12.7                                                                                                                           | Batteries                                                                                                                                                                                                                                                                                                                                                                                | 241                                                                                                                        | 18.1                                                                                                 | Synchronous generators                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 337                                                                                                   |

| 12.8                                                                                                                           | Cooling                                                                                                                                                                                                                                                                                                                                                                                  | 245                                                                                                                        | 18.2                                                                                                 | Synchronous torque                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 338                                                                                                   |

|                                                                                                                                | Problems                                                                                                                                                                                                                                                                                                                                                                                 | 248                                                                                                                        | 18.3                                                                                                 | The equivalent circuit of a synchronous generator                                                                                                                                                                                                                                                                                                                                                                                                                       | 338                                                                                                   |

| 13                                                                                                                             | Magnetism and                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            | 18.4                                                                                                 | Per-unit values and the short-                                                                                                                                                                                                                                                                                                                                                                                                                                          | 330                                                                                                   |

| 13                                                                                                                             | Magnetism and electromagnetism                                                                                                                                                                                                                                                                                                                                                           | 249                                                                                                                        |                                                                                                      | circuit ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 339                                                                                                   |

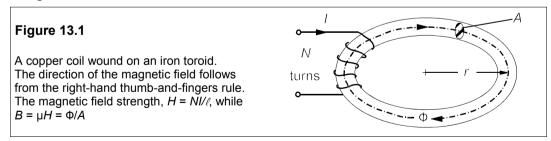

| 13.1                                                                                                                           | Magnetic units and quantities                                                                                                                                                                                                                                                                                                                                                            | 249                                                                                                                        | 18.5                                                                                                 | The generator under load                                                                                                                                                                                                                                                                                                                                                                                                                                                | 340                                                                                                   |

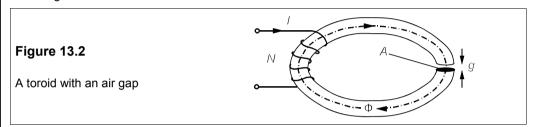

| 13.2                                                                                                                           | The magnetic circuit                                                                                                                                                                                                                                                                                                                                                                     | 251                                                                                                                        | 18.6<br>18.7                                                                                         | The generator on an infinite bus The construction of synchronous                                                                                                                                                                                                                                                                                                                                                                                                        | 341                                                                                                   |

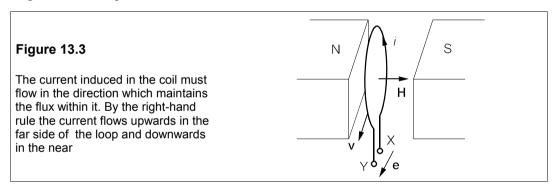

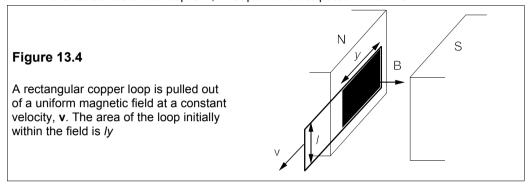

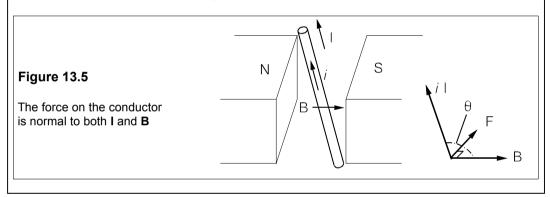

| 13.3                                                                                                                           | Faraday's law of electromagnetic                                                                                                                                                                                                                                                                                                                                                         | 0.50                                                                                                                       | 10.7                                                                                                 | machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 343                                                                                                   |

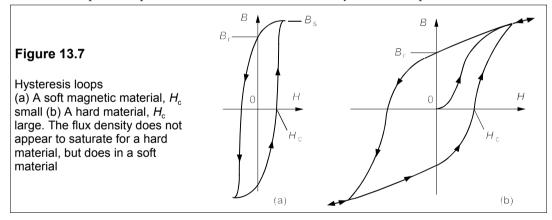

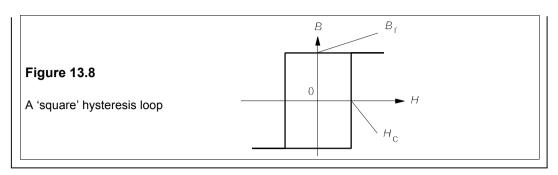

| 13.4                                                                                                                           | induction<br>Hysteresis                                                                                                                                                                                                                                                                                                                                                                  | 253<br>256                                                                                                                 | 18.8                                                                                                 | Synchronous motors                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 345                                                                                                   |

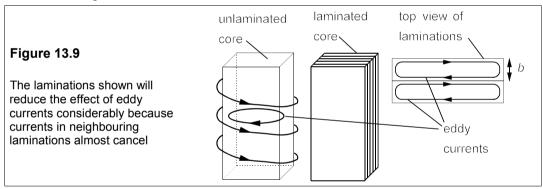

| 13.5                                                                                                                           | Eddy currents                                                                                                                                                                                                                                                                                                                                                                            | 258                                                                                                                        |                                                                                                      | Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 349                                                                                                   |

| 13.6                                                                                                                           | Inductors                                                                                                                                                                                                                                                                                                                                                                                | 259                                                                                                                        | 19                                                                                                   | Power electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 350                                                                                                   |

|                                                                                                                                | Problems                                                                                                                                                                                                                                                                                                                                                                                 | 259                                                                                                                        | 19<br>19.1                                                                                           | The three-phase bridge rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                        | 350                                                                                                   |

| 14                                                                                                                             | DC machines                                                                                                                                                                                                                                                                                                                                                                              | 261                                                                                                                        | 19.2                                                                                                 | Power semiconductor devices                                                                                                                                                                                                                                                                                                                                                                                                                                             | 352                                                                                                   |

|                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       |

|                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            | 19.3                                                                                                 | Power-control circuits using                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

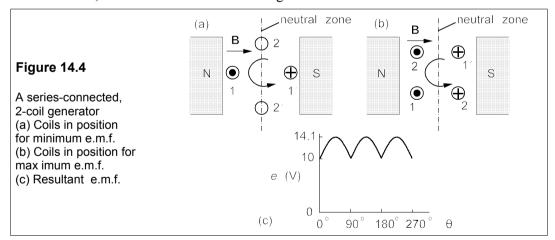

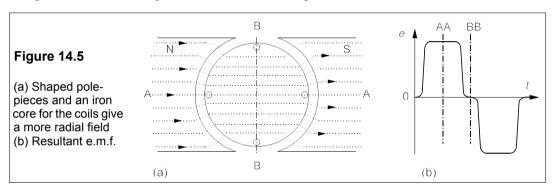

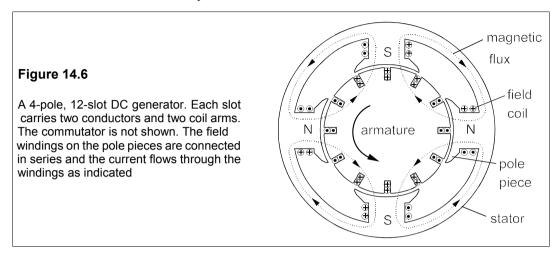

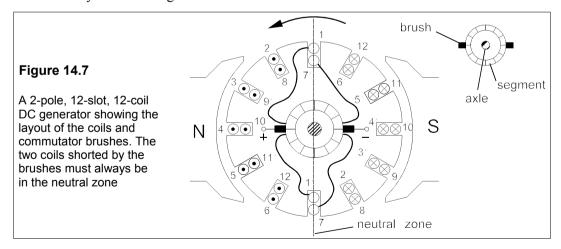

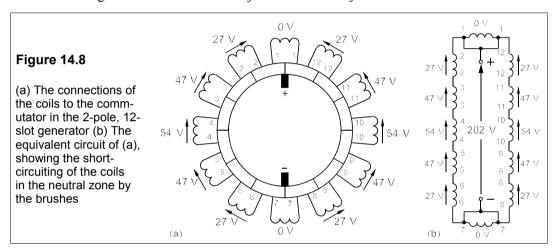

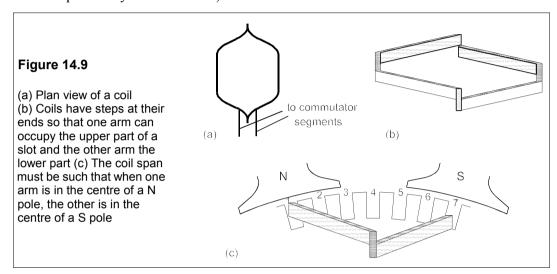

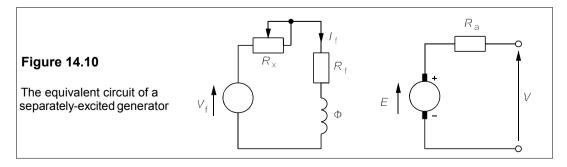

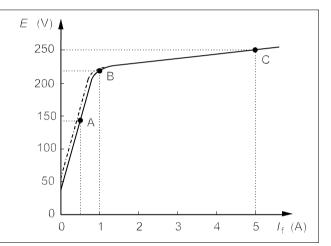

| 14.1<br>14.2                                                                                                                   | A prototype generator DC generators                                                                                                                                                                                                                                                                                                                                                      | 261<br>264                                                                                                                 |                                                                                                      | Power-control circuits using thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                 | 358                                                                                                   |

| 14.1<br>14.2<br>14.3                                                                                                           | A prototype generator<br>DC generators<br>DC motors                                                                                                                                                                                                                                                                                                                                      | 261<br>264<br>273                                                                                                          | 19.3<br>19.4                                                                                         | Power-control circuits using thyristors Motor control with power                                                                                                                                                                                                                                                                                                                                                                                                        | 358                                                                                                   |

| 14.1<br>14.2                                                                                                                   | A prototype generator<br>DC generators<br>DC motors<br>Efficiency and losses                                                                                                                                                                                                                                                                                                             | 261<br>264<br>273<br>282                                                                                                   |                                                                                                      | Power-control circuits using thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| 14.1<br>14.2<br>14.3                                                                                                           | A prototype generator<br>DC generators<br>DC motors                                                                                                                                                                                                                                                                                                                                      | 261<br>264<br>273                                                                                                          | 19.4                                                                                                 | Power-control circuits using thyristors Motor control with power electronics Problems                                                                                                                                                                                                                                                                                                                                                                                   | 358<br>362<br>368                                                                                     |

| 14.1<br>14.2<br>14.3                                                                                                           | A prototype generator<br>DC generators<br>DC motors<br>Efficiency and losses                                                                                                                                                                                                                                                                                                             | 261<br>264<br>273<br>282                                                                                                   | 19.4<br><b>20</b>                                                                                    | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic                                                                                                                                                                                                                                                                                                                                                              | 358<br>362<br>368<br><b>369</b>                                                                       |

| 14.1<br>14.2<br>14.3<br>14.4                                                                                                   | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase                                                                                                                                                                                                                                                          | 261<br>264<br>273<br>282<br>285<br><b>287</b>                                                                              | 19.4<br><b>20</b><br>20.1                                                                            | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers                                                                                                                                                                                                                                                                                                                               | 358<br>362<br>368                                                                                     |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1                                                                              | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity                                                                                                                                                                                                                                              | 261<br>264<br>273<br>282<br>285<br><b>287</b>                                                                              | 19.4<br><b>20</b>                                                                                    | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic                                                                                                                                                                                                                                                                                                                                                              | 358<br>362<br>368<br><b>369</b>                                                                       |

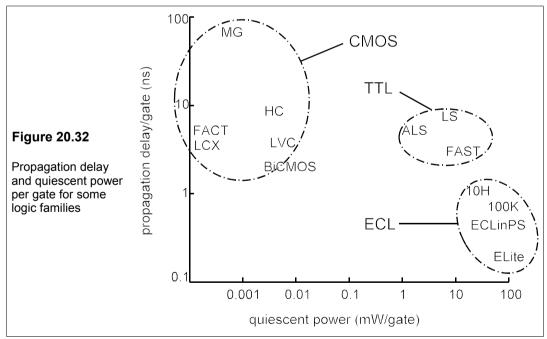

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1                                                                              | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads                                                                                                                                                                                                                               | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>287<br>290                                                                | 19.4<br><b>20</b><br>20.1<br>20.2<br>20.3                                                            | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs                                                                                                                                                                                                                                                                                 | 358<br>362<br>368<br><b>369</b><br>369<br>372<br>376                                                  |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1                                                                              | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity                                                                                                                                                                                                                                              | 261<br>264<br>273<br>282<br>285<br><b>287</b>                                                                              | 19.4<br><b>20</b><br>20.1<br>20.2<br>20.3<br>20.4                                                    | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems                                                                                                                                                                                                                                                            | 358<br>362<br>368<br><b>369</b><br>369<br>372<br>376<br>377                                           |

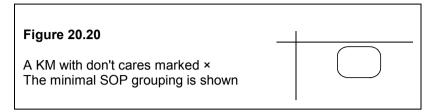

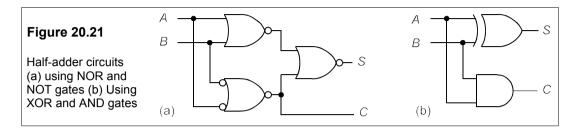

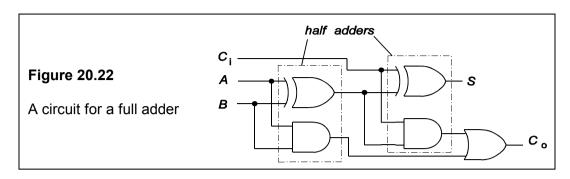

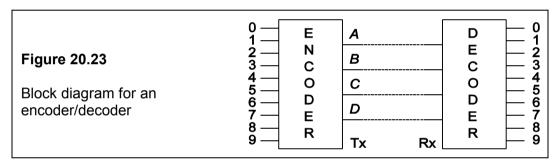

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3                                                              | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits                                                                                                                                                                    | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>287<br>290<br>293                                                         | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5                                                   | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms                                                                                                                                                                                                                                      | 358<br>362<br>368<br><b>369</b><br>369<br>372<br>376                                                  |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3                                                              | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-                                                                                                                                                                                  | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>287<br>290<br>293                                                         | 19.4<br><b>20</b><br>20.1<br>20.2<br>20.3<br>20.4                                                    | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation                                                                                                                                                                                            | 358<br>362<br>368<br><b>369</b><br>369<br>372<br>376<br>377                                           |

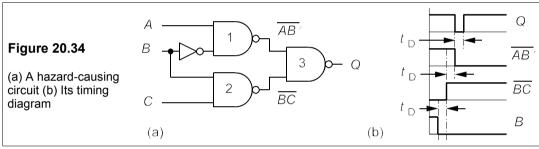

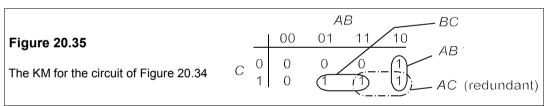

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3<br>15.4                                                      | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems                                                                                                                                                           | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>287<br>290<br>293<br>295<br>297                                           | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6                                           | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples                                                                                                                                                                         | 358<br>362<br>368<br><b>369</b><br>369<br>372<br>376<br>377<br>379<br>381<br>385                      |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3                                                              | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers                                                                                                                                             | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>287<br>290<br>293<br>295<br>297<br><b>298</b>                             | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8                           | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families                                                                                                                                                          | 358<br>362<br>368<br><b>369</b><br>369<br>372<br>376<br>377<br>379                                    |

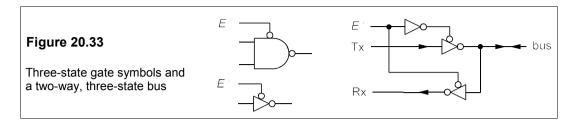

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3<br>15.4<br><b>16</b><br>16.1<br>16.2                         | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers The ideal transformer Transformer testing                                                                                                   | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>297<br>293<br>295<br>297<br><b>298</b><br>298<br>302                      | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6                                           | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families Practical aspects of logic                                                                                                                               | 358<br>362<br>368<br><b>369</b><br>372<br>376<br>377<br>379<br>381<br>385<br>390                      |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3<br>15.4<br><b>16</b><br>16.1<br>16.2<br>16.3                 | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers The ideal transformer Transformer testing Practical transformers                                                                            | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>287<br>290<br>293<br>295<br>297<br><b>298</b><br>302<br>308               | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10          | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families Practical aspects of logic integrated circuits Multiplexers and demultiplexers                                                                           | 358<br>362<br>368<br><b>369</b><br>369<br>372<br>376<br>377<br>379<br>381<br>385                      |

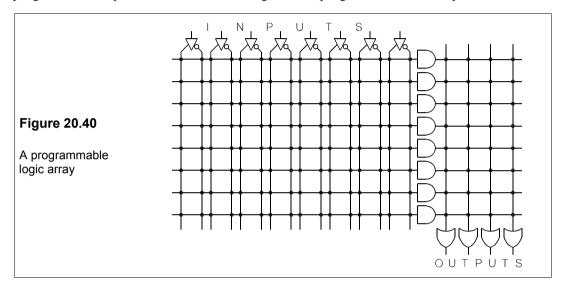

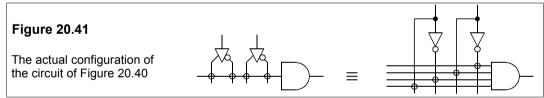

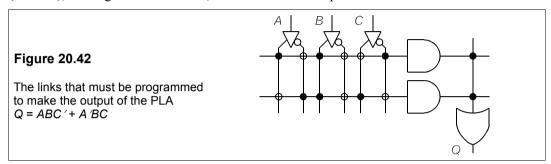

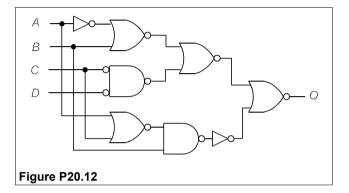

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3<br>15.4<br><b>16</b><br>16.1<br>16.2<br>16.3<br>16.4         | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers The ideal transformer Transformer testing Practical transformers Transformer design                                                         | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>297<br>293<br>295<br>297<br><b>298</b><br>298<br>302<br>308<br>310        | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10          | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families Practical aspects of logic integrated circuits Multiplexers and demultiplexers Programmable logic arrays                                                 | 358<br>362<br>368<br>369<br>369<br>372<br>376<br>377<br>379<br>381<br>385<br>390<br>393<br>397<br>399 |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3<br>15.4<br><b>16</b><br>16.1<br>16.2<br>16.3                 | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers The ideal transformer Transformer testing Practical transformers                                                                            | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>287<br>290<br>293<br>295<br>297<br><b>298</b><br>302<br>308               | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10          | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families Practical aspects of logic integrated circuits Multiplexers and demultiplexers                                                                           | 358<br>362<br>368<br>369<br>369<br>372<br>376<br>377<br>379<br>381<br>385<br>390<br>393<br>397        |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3<br>15.4<br><b>16</b><br>16.1<br>16.2<br>16.3<br>16.4<br>16.5 | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers The ideal transformer Transformer testing Practical transformers Transformer design Special types of transformer Problems                   | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>290<br>293<br>295<br>297<br><b>298</b><br>302<br>308<br>310<br>312<br>315 | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11 | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families Practical aspects of logic integrated circuits Multiplexers and demultiplexers Programmable logic arrays Problems  Sequential logic                      | 358 362 368 369 369 372 376 377 379 381 385 390 393 397 399 400 403                                   |

| 14.1<br>14.2<br>14.3<br>14.4<br>15.1<br>15.1<br>15.2<br>15.3<br>15.4<br>16.1<br>16.2<br>16.3<br>16.4<br>16.5                   | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers The ideal transformer Transformer testing Practical transformers Transformer design Special types of transformer Problems  Induction motors | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>297<br>293<br>295<br>297<br><b>298</b><br>302<br>308<br>310<br>312        | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11 | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families Practical aspects of logic integrated circuits Multiplexers and demultiplexers Programmable logic arrays Problems  Sequential logic Unclocked flip-flops | 358 362 368 369 369 372 376 377 379 381 385 390 393 397 399 400 403 403                               |

| 14.1<br>14.2<br>14.3<br>14.4<br><b>15</b><br>15.1<br>15.2<br>15.3<br>15.4<br><b>16</b><br>16.1<br>16.2<br>16.3<br>16.4<br>16.5 | A prototype generator DC generators DC motors Efficiency and losses Problems  Three-phase systems The generation of three-phase electricity Balanced loads Unbalanced loads Power measurement in three-phase circuits Problems  Transformers The ideal transformer Transformer testing Practical transformers Transformer design Special types of transformer Problems                   | 261<br>264<br>273<br>282<br>285<br><b>287</b><br>290<br>293<br>295<br>297<br><b>298</b><br>302<br>308<br>310<br>312<br>315 | 19.4<br>20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11 | Power-control circuits using thyristors Motor control with power electronics Problems  Combinational logic Binary and hexadecimal numbers Logic functions and Boolean algebra Logic ICs De Morgan's theorems Minterms and maxterms Karnaugh mapping and circuit minimisation Practical examples Logic families Practical aspects of logic integrated circuits Multiplexers and demultiplexers Programmable logic arrays Problems  Sequential logic                      | 358 362 368 369 369 372 376 377 379 381 385 390 393 397 399 400 403                                   |

Contents vii

| 21.5                                                                                                                    | Timers                                                                                                                                                                                                                                                                                                                                      | 415                                                                                                          | 26                                                                 | Fibre-optic communications                                                                                                                                                                                                                                     | 519                                                                              |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                         | Problems                                                                                                                                                                                                                                                                                                                                    | 417                                                                                                          | 26.1                                                               | Pros and cons of fibre-optics                                                                                                                                                                                                                                  | 519                                                                              |

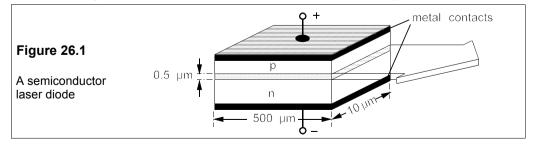

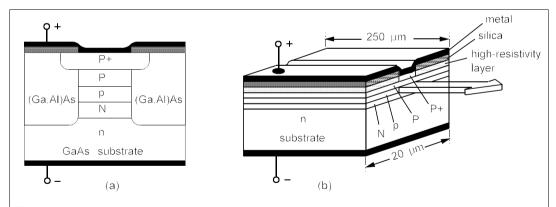

|                                                                                                                         |                                                                                                                                                                                                                                                                                                                                             |                                                                                                              | 26.2                                                               | The transmitter                                                                                                                                                                                                                                                | 520                                                                              |

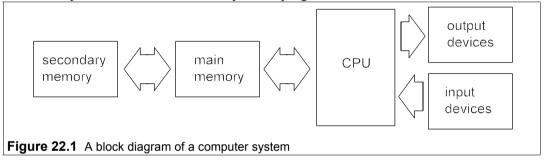

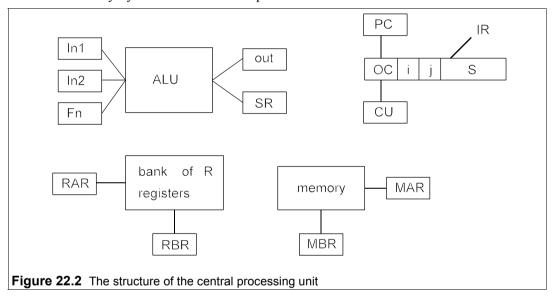

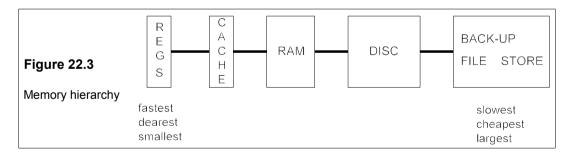

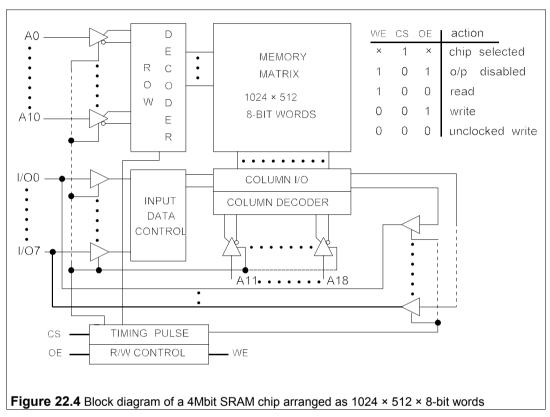

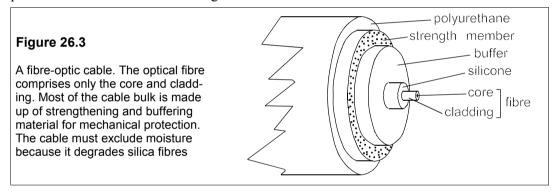

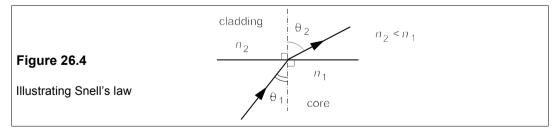

| 22                                                                                                                      | Computers                                                                                                                                                                                                                                                                                                                                   | 419                                                                                                          | 26.3                                                               | The channel: optical fibres                                                                                                                                                                                                                                    | 522                                                                              |

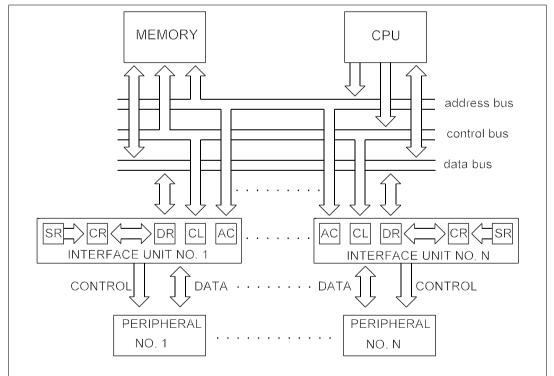

| 22.1                                                                                                                    | Computer architecture                                                                                                                                                                                                                                                                                                                       | 421                                                                                                          | 26.4                                                               | Optoelectronic signal detectors                                                                                                                                                                                                                                | 529                                                                              |

| 22.2                                                                                                                    | The CPU                                                                                                                                                                                                                                                                                                                                     | 421                                                                                                          | 26.5                                                               | The ultimate performance of                                                                                                                                                                                                                                    |                                                                                  |

| 22.3                                                                                                                    | Memory                                                                                                                                                                                                                                                                                                                                      | 424                                                                                                          |                                                                    | optical receivers                                                                                                                                                                                                                                              | 532                                                                              |

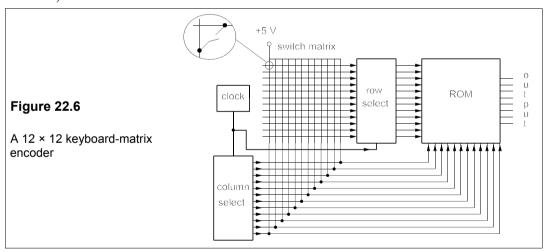

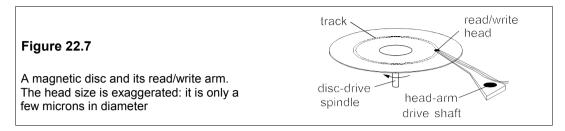

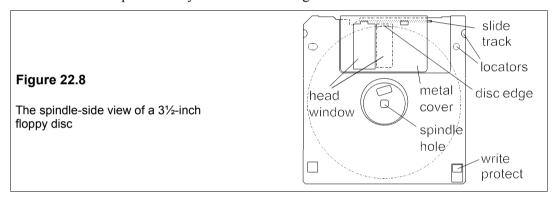

| 22.4                                                                                                                    | Input and output devices                                                                                                                                                                                                                                                                                                                    | 428                                                                                                          |                                                                    | Problems                                                                                                                                                                                                                                                       | 533                                                                              |

| 22.5                                                                                                                    | Computer networks                                                                                                                                                                                                                                                                                                                           | 436                                                                                                          |                                                                    |                                                                                                                                                                                                                                                                |                                                                                  |

| 22.6                                                                                                                    | Programming languages                                                                                                                                                                                                                                                                                                                       | 439                                                                                                          | 27                                                                 | Telephony                                                                                                                                                                                                                                                      | 535                                                                              |

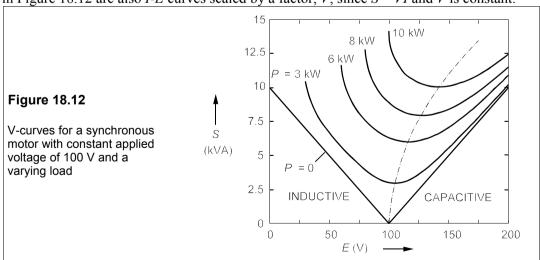

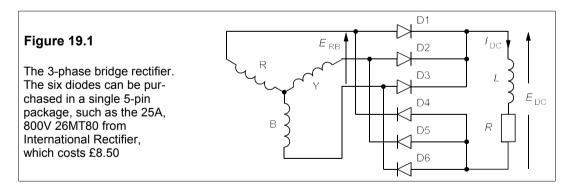

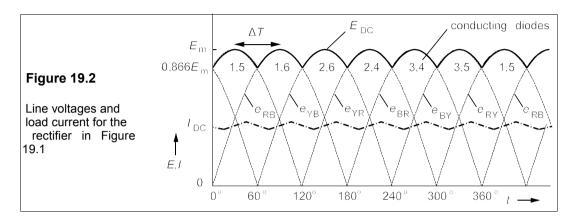

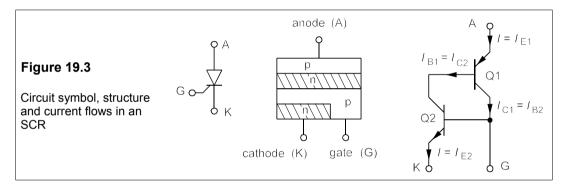

| 0                                                                                                                       | r rogramming languages                                                                                                                                                                                                                                                                                                                      | .00                                                                                                          | 27.1                                                               | Signalling                                                                                                                                                                                                                                                     | 536                                                                              |